東大 生研、パワー半導体スイッチング損失低減技術の適用範囲を約5倍に拡大

2025年03月17日19時08分 / 提供:マイナビニュース![]()

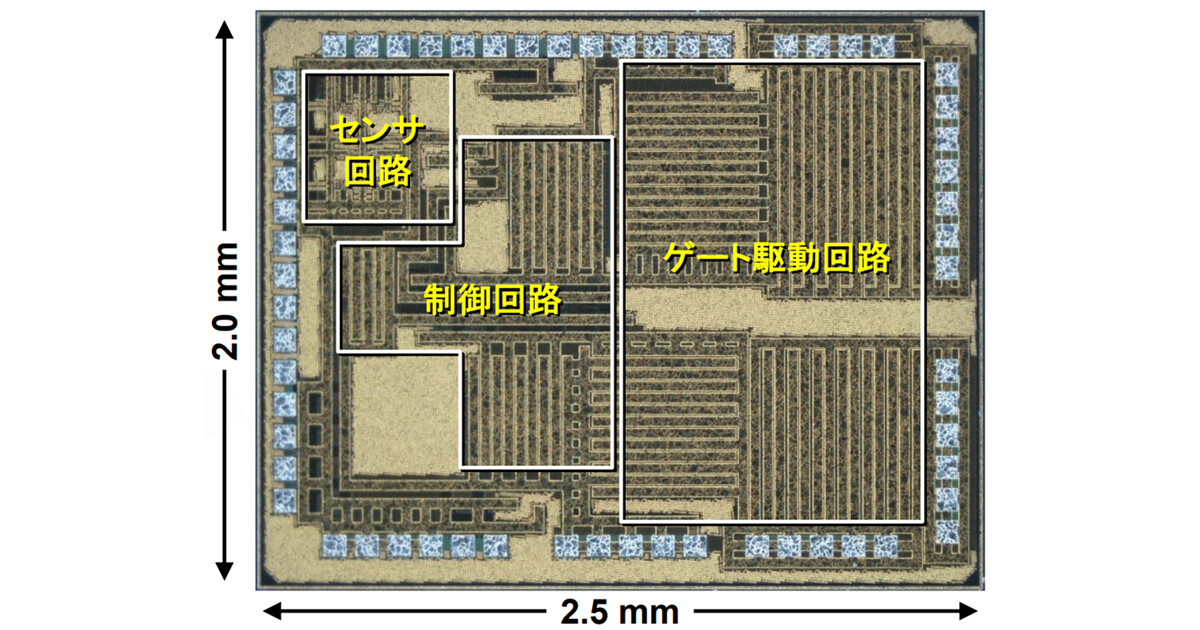

東京大学 生産技術研究所(東大 生研)と芝浦工業大学(芝浦工大)は3月17日、パワー半導体のスイッチング損失を自動で低減するとして2023年3月に発表していたゲート駆動ICチップについて、現在パワーデバイス市場で広く採用される“3本足パッケージ”への適用を可能にし、同チップの適用範囲の大幅な拡大に成功したことを発表した。

この発表に際し東大 生研はオンラインで記者説明会を実施。開発を主導した東大 生研の高宮真教授が登壇し、今回発表された新技術のメカニズムや、エネルギー利用の観点からパワーデバイスへの注目が集まる将来の社会に与えるインパクトについて説明した。

なお今回の研究成果は、東大 生研の高宮教授、同・梁耀淦特任研究員、芝浦工大 工学部の畑勝裕准教授らの研究チームによるもので、新エネルギー・産業技術総合開発機構(NEDO)の委託事業「省エネエレクトロニクスの製造基盤強化に向けた技術開発事業」により得られた。また詳細は、3月16日から20日まで米・アトランタで開催されている国際学会「IEEE Applied Power Electronics Conference and Exposition (APEC) 2025」にて発表された。

○2023年に発表した損失低減技術の適用範囲を5倍に拡大

.